# Architecture Description Languages

Edited by Pierre Dissaux Mamoun Filali Amine Pierre Michel

### ARCHITECTURE DESCRIPTION LANGUAGES

#### IFIP – The International Federation for Information Processing

IFIP was founded in 1960 under the auspices of UNESCO, following the First World Computer Congress held in Paris the previous year. An umbrella organization for societies working in information processing, IFIP's aim is two-fold: to support information processing within its member countries and to encourage technology transfer to developing nations. As its mission statement clearly states,

*IFIP's mission is to be the leading, truly international, apolitical organization which encourages and assists in the development, exploitation and application of information technology for the benefit of all people.*

IFIP is a non-profitmaking organization, run almost solely by 2500 volunteers. It operates through a number of technical committees, which organize events and publications. IFIP's events range from an international congress to local seminars, but the most important are:

- The IFIP World Computer Congress, held every second year;

- Open conferences;

- Working conferences.

The flagship event is the IFIP World Computer Congress, at which both invited and contributed papers are presented. Contributed papers are rigorously refereed and the rejection rate is high.

As with the Congress, participation in the open conferences is open to all and papers may be invited or submitted. Again, submitted papers are stringently refereed.

The working conferences are structured differently. They are usually run by a working group and attendance is small and by invitation only. Their purpose is to create an atmosphere conducive to innovation and development. Refereeing is less rigorous and papers are subjected to extensive group discussion.

Publications arising from IFIP events vary. The papers presented at the IFIP World Computer Congress and at open conferences are published as conference proceedings, while the results of the working conferences are often published as collections of selected and edited papers.

Any national society whose primary activity is in information may apply to become a full member of IFIP, although full membership is restricted to one society per country. Full members are entitled to vote at the annual General Assembly, National societies preferring a less committed involvement may apply for associate or corresponding membership. Associate members enjoy the same benefits as full members, but without voting rights. Corresponding members are not represented in IFIP bodies. Affiliated membership is open to non-national societies, and individual and honorary membership schemes are also offered.

## ARCHITECTURE DESCRIPTION LANGUAGES

IFIP TC-2 Workshop on Architecture Description Languages (WADL), World Computer Congress, Aug. 22-27, 2004, Toulouse, France

Edited by

**Pierre Dissaux** TNI-Europe France

#### Mamoun Filali-Amine (Chair)

IRIT/FERIA France

**Pierre Michel** ONERA/FERIA France

**François Vernadat** LAAS/FERIA France

Library of Congress Cataloging-in-Publication Data

A C.I.P. Catalogue record for this book is available from the Library of Congress.

Architecture Description Languages Edited by Pierre Dissaux, Mamoun Filali-Amine, Pierre Michel and François Vernadat

p.cm. (The International Federation for Information Processing)

ISBN: (HB) 0-387-24589-8 / (eB00K) 0-387-24590-1 Printed on acid-free paper.

Copyright © 2005 by International Federation for Information Processing.

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher [Springer Science+Business Media, Inc., 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now know or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if the are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed in the United States of America.

9 8 7 6 5 4 3 2 1 SPIN 11391616 (HC) / 11391999 (eBook) springeronline.com

### Contents

Preface

| Committee Members                                                                                                                                                                                                               | ix |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tutorial                                                                                                                                                                                                                        |    |

| An overview of the SAE Architecture Analysis & Design Language<br>(AADL) Standard: a basis for model-based architecture-driven<br>embedded systems engineering<br><i>Peter H. Feiler, Bruce Lewis, Steve Vestal, Ed Colbert</i> | 3  |

| Session 1: Models and Analysis                                                                                                                                                                                                  |    |

| Deploying QoS Contracts in the Architectural Level<br>Sidney Ansaloni, Alexandre Sztajnberg, Romulo Cerqueira,<br>Orlando Loques                                                                                                | 19 |

| Hierarchical Composition and Abstraction in Architecture Models<br>Pam Binns, Steve Vestal                                                                                                                                      | 35 |

| Pattern-Based Analysis of an Embedded Real-time System<br>Architecture<br>Peter H. Feiler, David P. Gluch, John J. Hudak, Bruce A. Lewis                                                                                        | 51 |

vii

| An ADL Centric Approach for the Formal Design of Real-Time<br>Systems<br>Sébastien Faucou, Anne-Marie Déplanche, Yvon Trinquet                                                                                                     | 67  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Session 2: Specification and Design                                                                                                                                                                                                |     |

| SafArchie Studio: ArgoUML Extensions to Build Safe Architectures<br>Olivier Barais, Laurence Duchien.                                                                                                                              | 85  |

| Enhancing the Role of Interfaces in Software Architecture Description<br>Languages (ADLs)<br>Seamus Galvin, Chris Exton, Finbar McGurren                                                                                           | 101 |

| How ADLs can help in adapting the CORBA Component Model to<br>Real-Time Embedded Software Design<br>Sylvain Robert, Vincent Seignole, Sébastien Gérard, Stéphane<br>Ménoret, Virginie Watine, Ansgar Radermacher, François Terrier | 117 |

| UML2 as an ADL hierarchichal hardware modeling<br>Arnaud Cuccuru, Philippe Marquet, Jean-Luc Dekeyser                                                                                                                              | 133 |

| Session 3: Domain Specific Architecture Description Languages                                                                                                                                                                      |     |

| Specification of Intel IA-32 using an Architecture Description<br>Language<br>Jeff Bastian, Soner Onder                                                                                                                            | 151 |

| COTRE as an AADL Profile<br>Patrick Farail, Pierre Gaufillet                                                                                                                                                                       | 167 |

| EAST-ADL an Architecture Description Language, Validation and Verification Aspects<br>Vincent Debruyne, Françoise Simonot-Lion, Yvon Trinquet                                                                                      | 181 |

| Building Tool Suite for AADL<br>Jean-François Tilman                                                                                                                                                                               | 197 |

Author Index

#### Preface

These proceedings record the papers presented at the Workshop on Architecture Description Languages held in the city of Toulouse in the south of France.

The aim of an ADL (Architecture Description Language) is to formally describe software and hardware architectures. Usually, an ADL describes components, their interfaces, their structures, their interactions (structure of data flow and control flow) and the mappings to hardware systems. A major goal of such descriptions is to allow analysis with respect to several aspects like timing, safety, reliability, ... This workshop has provided a forum for practitioners and researchers to discuss recent development around ADLs. A feature of this workshop has been to brought different communities, from e.g., avionics and space embedded systems, automotive embedded systems, distributed systems, to confront their approaches, to discuss their emerging standards, and to share their respective knowledge.

Toulouse and Brest, September 2004

Pierre Dissaux, Mamoun Filali Amine, Pierre Michel, François Vernadat Editors

#### **Program Committee**

- Eric Conquet, ESA/ESTEC, France

- Anne-Marie Deplanche, IRCCYN, France

- Pierre Dissaux, TNI-Europe, France

- Jean-Pierre Elloy, IRCCYN, France

- Patrick Farail, EADS Airbus, France

- Jean-Marie Farines, DAS UFSC, Brazil

- Peter Feiler, Carnegie Mellon Univ./SEI, USA

- Mamoun Filali Amine, IRIT/FERIA, France

- Pierre Gaufillet, EADS Airbus, France

- Clegg Kester, Univ. of York, UK

- Bruce Lewis, US Army/ AMCOM, USA

- Pierre Michel, ONERA/FERIA, France

- Alek Radjenovic, Univ. of York, UK

- Françoise Simonot-Lion, LORIA, France

- François Terrier, CEA-LIST, France

- Jean-François Tilman, AXLOG Ingénierie, France

- François Vernadat, LAAS/FERIA, France

- Steve Vestal, Honeywell Laboratories, USA

- Sergio Yovine, VERIMAG, France

- Andre Windisch, EADS, Germany

### Referees

We are grateful for the following people who aided the program committees in the reviewing of papers.

| Jean-Luc Béchennec<br>Jean-Paul Bodeveix |                            | France<br>France |

|------------------------------------------|----------------------------|------------------|

| oodaa a daa bodooon                      | IRIT/FERIA<br>IRCCYN       |                  |

| Anne-Marie Déplanche                     |                            | France           |

| Pierre Dissaux                           | TNI-Europe                 | France           |

| Khalil Drira                             | LAAS                       | France           |

| Jean-Pierre Elloy                        | IRCCYN                     | France           |

| Patrick Farail                           | EADS Airbus                | France           |

| Jean-Marie Farines                       | DAS UFSC                   | Brazil           |

| Peter Feiler                             | Carnegie Mellon Univ. /SEI | USA              |

| Mamoun Filali                            | IRIT/FERIA                 | France           |

| Pierre Gaufillet                         | EADS Airbus                | France           |

| Clegg Kester                             | Univ of York               | UK               |

| Bruce Lewis                              | US Army / AMCOM            | USA              |

| Christophe Lohr                          | Concordia University       | Canada           |

| Philippe Mauran                          | IRIT/FERIA                 | France           |

| Pierre Michel                            | CERT/FERIA                 | France           |

| Francisco Moo Mena                       | LAAS                       | France           |

| Alek Radjenovic                          | Univ of York               | UK               |

| Xavier Rebeuf                            | LORIA                      | France           |

| Pierre-Olivier Ribet                     | LAAS/FERIA                 | France           |

| Pascal Sainrat                           | IRIT                       | France           |

| Pierre de SaquiSannes                    | ENSICA                     | France           |

| Françoise Simonot-Lion                   | LORIA                      | France           |

| François Terrier                         | CEA-LIST                   | France           |

| Jean-François Tilman                     | AXLOG Ingénierie           | France           |

| François Vernadat                        | LAAS/FERIA                 | France           |

| Steve Vestal                             | Honeywell Laboratories     | USA              |

| Sergio Yovine                            | VERIMAG                    | France           |

| Andre Windisch                           | EADS                       | Germany          |

|                                          |                            | J                |

## TUTORIAL

### An Overview of the SAE Architecture Analysis & Design Language (AADL) Standard: A Basis for Model-Based Architecture-Driven Embedded Systems Engineering

Peter H. Feiler<sup>1</sup>, Bruce Lewis<sup>2</sup>, Steve Vestal<sup>3</sup> and Ed Colbert<sup>4</sup>

<sup>1</sup>Software Engineering Institute, USA, <u>phf@sei.cmu.edu</u> <sup>2</sup>US Army AMCOM, USA, <u>bruce.lewis@sed.redstone.army.mil</u> <sup>3</sup>Honeywell Laboratories, USA, <u>Steve.Vestal@honeywell.com</u> <sup>4</sup>Absolute Software, USA, <u>colbert@abssw.com</u>

www.aadl.info email: info@aadl.info

- Abstract: Architecture Description Languages provide significant opportunity for the incorporation of formal methods and engineering models into the analysis of software and system architectures. A standard is being developed for embedded real-time safety critical systems which will support the use of various formal approaches to analyze the impact of the composition of systems from hardware and software and which will allow the generation of system glue code with the performance qualities predicted. The SAE AADL standard (International Society for Automotive Engineers (SAE) Architecture Analysis & Design Language) is based on the MetaH language developed under DARPA and US Army funding and on the model driven architectural based approach demonstrated with this technology over the last 12 years. The SAE AADL standard is aimed at supporting avionics, space, automotive, robotics and other real-time concurrent processing domains including safety critical applications.

- Keywords: Architecture Analysis & Design Language; AADL; architecture description language; computer architecture; computer modeling; computer analysis; embedded systems; model based development; SAE; software architecture; system architecture.

#### 1. INTRODUCTION

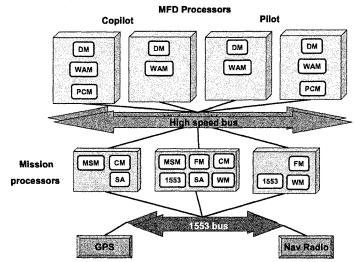

The International Society for Automotive Engineers (SAE) Architecture Analysis & Design Language (AADL) is a textual and graphical language used to design and analyze the software and hardware architecture of realtime systems and their performance-critical characteristics. It is aimed at supporting the avionics, aerospace, and automotive industry. The language is used to describe the structure of such systems as an assembly of software components mapped onto an execution platform. The language can describe functional interfaces to components (such as data inputs and outputs) and performance-critical aspects of components (such as timing). The language can describe how components interact, such as how data inputs and outputs are connected, how and when components are executed, and how application software components are allocated to execution platform components. The language can also describe the dynamic behavior of the runtime architecture by supporting the modeling concept of operational modes and mode The language is designed to be extensible to accommodate transitions. analyses of additional runtime architectures that the core language does not completely support. Extensions can take the form of new properties and analysis specific notations that can be associated with components.

The AADL was developed under the auspices of the International Society for Automotive Engineers (SAE). The AADL is developed for embedded systems that have challenging resource (size, weight, power) constraints, that have challenging and strict real-time response requirements that must tolerate faults, that have specialized input/output hardware, and that must be certified to high levels of assurance. Intended fields of application are avionics systems, flight management, engine and power train control systems, certain medical devices, industrial process control equipment, and space applications. The AADL addresses system of systems architectures, supporting integration of embedded systems into higher level systems.

The language can describe important performance-critical aspects such as timing requirements, fault and error behaviors, time and space partitioning, and safety and certification properties. Such a description allows a system designer to perform analyses of the composed components and systems such as system schedulability, sizing analysis, and safety analysis. From these analyses, the designer can evaluate architectural tradeoffs and changes. Since the AADL supports multiple and extensible analysis approaches, it provides the ability to analyze the cross cutting impacts of change in the architecture in one specification using multiple analysis tools. The AADL specification language has been designed to be further used with proper tool support to generate the code needed to integrate the system components and build a system executive. Since the models and the architecture specification drive the design and implementation, they can be maintained to permit model driven architecture based changes throughout the system lifecycle.

#### 2. Background

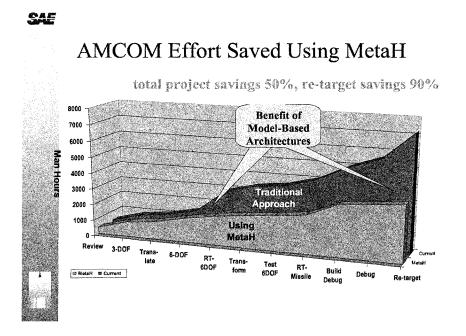

The AADL is based on experiences in the use of DARPA funded ADL efforts, in particular MetaH developed by Honeywell []. A number of organizations have used MetaH in prototypical system developments, including Boeing, US Army, and the SEI. The case study of a pilot application of the MetaH technology by the U.S. Army AMCOM SED laboratory to missile guidance systems produced some insights into the potential cost savings of an architecture-driven approach. An existing missile guidance system, implemented in Jovial, was reengineered to run on a new hardware platform and to fit into generic missile reference architecture []. As part of the reengineering effort the system was modularized and translated into Ada95. The task architecture consisting of 12-16 concurrent tasks was represented as a MetaH model and the implementation generated automatically from the MetaH model and the Ada95 coded application components. The resulting system consisted of 12,000 source lines of application component code, 3000 lines of MetaH executive generated from the MetaH model, and 3000 lines of code representing MetaH kernel services. The engineers doing the reengineering work made a conservative estimate of effort required to reengineer the system into a pure Ada95 implementation and validated the estimate with the prime contractor who implemented the missile. The cost savings of 40% (prime estimated 66%) was obtained for reengineering to a different language and platform, then the time critical software was ported to multiple processor/0S/compiler platforms at a cost savings of 90% per port.

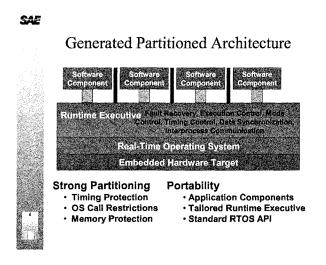

MetaH demonstrated the practicality of using an Architecture Description Language (ADL) as core modeling notation for providing analysis capabilities of several performance-critical quality attribute dimensions such as schedulability, dependability, and safety-critical concerns. The MetaH toolset demonstrated the capability of not only supporting system analysis, but also automatic generation of glue code in form of a system executive that performs all task binding, dispatching, and inter-task communication with application components as "plug-ins" into this infrastructure. This separation of concerns allows application developers to focus on domain functionality, while a software system architect can focus on achieving system-level performancecritical quality attributes.

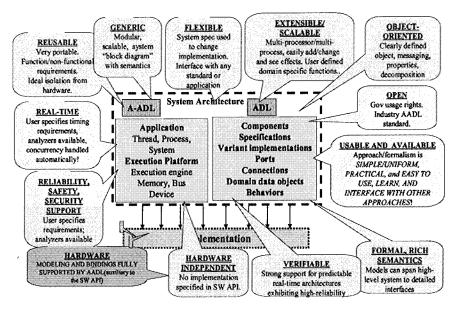

3. An Analyzable Software System Architecture Description Notation

The AADL has been designed to be a basis for model-based analysis and generation of embedded systems, i.e., embedded and system of systems engineering driven by an architecture that is reflected in the models and maintained throughout the system life cycle []. The notation has been designed as an extensible core language with well defined semantics and both a graphical and textual presentation. The core language supports modeling in several architecture views [7] and addresses timing and performance analyses through explicit modeling of application system and execution platform components and their binding as well as precisely defined concurrency and interaction semantics and timing/performance properties. The extension mechanisms permit properties to be introduced that are specific to additional architecture analyses in terms of other quality attributes such as reliability, security, etc, as were demonstrated with MetaH, and new analysis approaches. In this section we introduce to core language and in the next section we discuss the extension capability.

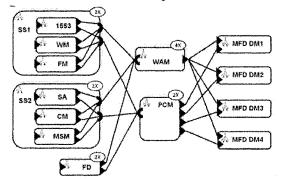

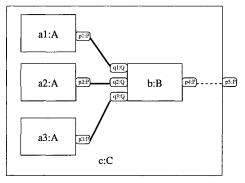

The focus of the AADL is to model the software system architecture in terms of an application system bound to an execution platform. The architecture is modeled in terms of hierarchies of components, whose interaction is represented by connections. Components have a component type that represents its externally visible interface and other characteristics, i.e., represents a component specification, and one or more implementations. A component implementation in the AADL may represent application source text and may be decomposed into an interconnected set of subcomponents that are instances of other component types and implementations. Generalization of components is supported in that component types and implementations can be expressed as extensions of other component types and implementations.

To support modeling of execution platforms four categories of components have been introduced: processor as a virtual machine that schedules and executes units of concurrent execution (threads) according to a specified scheduling protocol and may support space partitioning through protected address spaces; memory as a storage abstraction that can hold data and/or code; bus as a connector abstraction between execution platform components, and a *device* as an abstraction of an active component that an application system can interact with and a processor executing software may require The execution platform components may represent access to via a bus. hardware components or abstract execution platform components, whose implementations may represent virtual machines that are implemented in terms of another execution platform, with the bindings finally resolving to Each execution platform category has a number of actual hardware. predefined properties such as thread and process swap time or scheduling protocol for processors. The core AADL predefines such properties and an initial set of acceptable property value that can be extended. For example, new scheduling protocols can be introduced through a property extension mechanism.

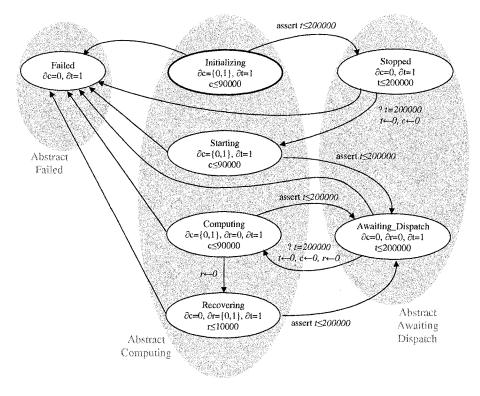

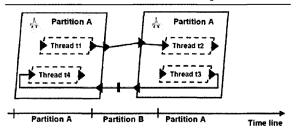

Application system modeling is supported through two groups of component categories. The first group focuses on the runtime behavior of a system and consists of: *thread* as basic unit of concurrent execution which can be abstracted into *thread groups*; and *process* as unit of protected address space. Threads are contained in processes and have one of a set of predefined dispatch protocol property values or one introduced through the property extension mechanism. Predefined dispatch protocols include periodic, aperiodic, sporadic, and background. Threads have separate execution entrypoints into their associated source text for initialization, nominal execution, and recovery. In case of nominal execution server threads may have multiple entrypoints defined as server subprogram entrypoints. The process load, thread dispatch and scheduling semantics are defined using a hybrid automaton notation.

The second group focuses on the source text of a system and consists of: *package* as unit of source text; and *data* component as passive application data. The package category allows the modeler to represent the source text decomposition structure to a level of detail that is appropriate to the modeling effort. The data component category supports representing data types and class abstractions in the source text as necessary for architecture models. The data type is used to type ports (see below), to specify subprogram parameter types, and to type shared data component instances. The component type extension mechanism can model type inheritance. Subprogram features (see

below) in component types can represent class methods and accessors of data component declared as sharable with a specified concurrency control protocol. Required access to sharable data component instances is specified in a *requires* subclause of a component type.

A final component category supports hierarchical composition and consists of: *system* as a unit whose implementations can contain execution platform components, application system components and other system instances.

The AADL supports modeling of three kinds of interactions between components: directional flow of data and/or control through data, event, and event data port connections; call/return interaction on subprogram entrypoints; and through access to a shared data component (see data component above).

Threads, processors, and devices, and their enclosing components (process and system) have in ports and out ports declared. Data ports communicate unqueued state data, event ports communicate events that are raised in their implementation, their associated source text, or actual hardware, and event data ports represent queued data whose arrival can have event semantics. Arrival of an event at a thread results in the dispatch of that thread – with semantics defined via property values and hybrid automata for event arrival while the thread is active. For data port connections data is communicated upon execution completion (immediate connection with the effect of midframe communication for periodic threads) or upon thread deadline (delayed connection with the effect of phase delay for periodic threads).

The data and event data ports appear to the application source text as data variables – in ports as data variables where input is found when a thread is dispatched, and out ports as variables into which output to be communicated to other components is placed for transfer at well-defined points. In other words, the application source text of a component has no knowledge of the components it interacts with. The interaction connection is defined as part of the AADL description, and appropriate runtime executive code can be generated for thread dispatching and communication.

Subprogram entrypoints are defined in component types as provided and required entrypoints. At the level of components representing source text they represent procedures/functions that are called sequentially. At the level of concurrent components they represent synchronous call/return between two concurrency units (client subprogram calling a server subprogram).

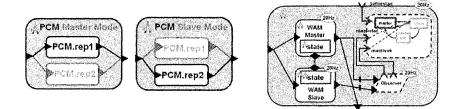

Components can have modes. Modes represent alternative configurations of the component implementation with only one mode being active at a time. At the level of system and process a mode represents possibly overlapping (sub-) sets of active threads and port connections, and alternative configurations of execution platform components, as well as alternative bindings of application components to execution platform components. Mode change behavior is specified as a state transition diagram whose states are the modes and the transitions are triggered by events. Thus, the AADL can model dynamically changing behavior of statically known thread and port communication topologies bound to statically known execution platform topologies. Modes can also be declared for sources text components. This permits mode-specific property values to be declared in situations where the thread and connection architecture does not change, but the thread internal behavior changes, e.g., it has different worst-case execution times under different modes. Such more detailed modeling of application systems allows for less conservative analysis such as schedulability analysis.

The AADL has the following basic fault handling model. Runtime faults may be handled within source text components through mechanisms that are part of the source language runtime environment. For faults not handled at that level or propagated by the source text a thread is given an opportunity to recover and continue with the next dispatch through a recovery entrypoint. Thread unrecoverable errors are propagated as error events. The modeler of a particular application system indicates through event connections where the error event is propagated to, and mode change behavior descriptions indicate actions taken in response to error events.

The AADL also supports other behavior specifications. It supports specification of sequential execution paths within threads to represent control flow within a thread in more detail. It supports specification of expected invocation patterns on subprogram entrypoints that can be checked against actual invocations. It supports specification of expected event port trigger patterns for a port collection, i.e., a lower-level control flow protocol represented by a collection of event port connections that externally is viewed as a single event connection. It supports flow specification to support end-to-end flow analysis of data and control.

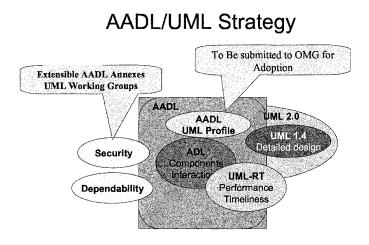

In summary, the core AADL supports modeling of application systems and execution platforms as interacting components with specific semantics and bindings. Such systems are configurable in that components have multiple implementations. Semantics defined as part of the component categories and their predefined properties address timing and resource consumption as well as interaction consistency in terms of matching port types and data communicated through the ports. Behavior descriptions allow for model checking of behaviors as well as mode(state)-specific analyses with less conservative results. The core language does not provide properties and semantics for all possible architecture analyses. Instead the AADL has been made extensible both in terms of language notation and in terms of standard annexes to accommodate further analyses. Annexes that will follow the initial core standard include language extensions such as ability to provide error modeling for various dependability analysis, a UML profile, an XML interchange format, and an Ada and C implementation annex. Additional annexes are planned for more detailed component behavior modeling, ARINC 653 and POSIX implementation, constraints etc.

## 4. An Extensible Software System Architecture Description Notation

The AADL has been made extensible in three respects. First, modelers can define an extensible set of component specifications in form of component types and implementations by making use of the extension mechanism discussed in the previous section. Second, the language itself can be extended through the ability to introduce new properties and extend the set of valid property values for existing properties. Third, the AADL draft standard includes its specification as a UML profile.

The AADL provides a library concept for organizing component type and implementation declarations. It provides a name scope, thus, facilitates independent development of major subsystems. Furthermore, the component extension mechanism allows modelers to define components and generalizations and specializations of other components.

The AADL currently supports the introduction of new properties extend the set of valid values, and associate them with existing component categories, ports, and connections through property extension sets. No specific notational capability is provided are part of the AADL to describe the semantic meaning of such properties, e.g., in terms of reliability characteristics. Instead, providers of such extension sets can use notations such as the hybrid automaton notation used in the definition of the core language, or resort to English text or other more precise notations to describe the formal model underlying a particular analysis to which the properties represent input.

In many cases it is desirable to express constraints on properties – such as a constraint that the sum of mass property values of any subcomponent with a mass does not exceed a certain maximum. We could consider extending the AADL to explicitly support a constraint language. At this time constraints can be introduced through properties with string values, whose meaning is only understood by constraint analysis tools.

The AADL can be viewed as a modeling notation that can be completed with notations tailored to the specific goals of a particular modeling view and analysis. Such complementary notations can be introduced through stringvalues properties as suggested above. Alternatively, additional modeling views and semantics addressing certain analyses can be expressed in terms of a UML sublanguage model. This approach is possible because we have developed a UML profile of the AADL as part of the draft standard.

#### 5. Status of the AADL as a Standard

The AADL standard has been in the works since 1999 with a balloted requirements document in 2000. The standard was approved for publication by the SAE in September of 2004. The specification of the AADL has been aligned with the OMG UML standard to benefit from its large practitioner base. The emerging UML2.0 standard is considered a partner in crime rather than competition. The UML profile of the AADL, which after being approved as an annex of the SAE standard, will be submitted for acceptance to the OMG to be part of their standard suite.

The standard provides a means for the commercial production of tools with a common AADL language interface. The UML profile, a specialization providing AADL semantics, will allow the application of formal analysis and code generation tools through a UML graphical specification, enabling the use of currently available UML tools for specification. We also will provide an XML specification for the AADL language now that the first version of the language standard is completed. These capabilities will provide an early interface for developing new analysis approaches.

The AADL Standardization Subcommittee also has a liaison relationship with a French research consortium, COTRE, headed by Airbus. COTRE has adopted the AADL for research into new tools, development and analysis methods to support aviation system development requirements. The AADL plays a significant role in a future software and systems development approach described by Airbus and COTRE in a recent paper[]. Other US and European companies and agencies are evaluating and experimenting with MetaH and the AADL.

Architecture based, model driven approaches are also beginning to appear in the general software engineering domain. UML 2.0, the Model Driven Architectures Initiative [], will provide a new layer to UML to directly support a generalized model driven architecture based approach. It is expected that multiple profiles for different domains will be defined as specializations of UML 2.0. UML 2.0 is expected to be released soon. The AADL UML profile will incorporate new architecture description capabilities from UML 2.0 when it is released.

#### The Model Driven Architecture (MDA) Initiative

- Based on the success of UML, the OMG has formulated a vision of a method of software development based on the use of models

- Key characteristic of MDA:

- The focus and principal products of software development are models rather than programs

- "The design is the implementation" (i.e. UML as both a modeling and an implementation language)

- UML plays a crucial role in MDA

- Automatic code generation from UML models

- Executable UML models

- Requires a more precise definition of the semantics of UML (UML 2.0)

Source: Bran Selic, Rational

The University of Southern California, Center for Software Engineering, lead by Barry Boehm, has announced the development of Model-Based Architecting and Software Engineering (MBASE) approach []. This approach currently is being developed to be compatible with several Architecture Description Languages, one being the AADL.

#### 6. Summary

The AADL has been designed to specifically support the development of large-scale systems through model-based architecture-driven software systems engineering by providing an analyzable architecture description language with well defined semantics. Its roots are in more than a decade's research in architecture description languages with an emphasis on concepts that address performance-critical embedded systems concerns, in particular timing and performance. The standard has been made extensible to permit inclusion of other performance-critical quality attribute concerns through annexes, without bloating the core standard. This permits new analyses to be supported in the future as they emerge from research, e.g., in the area of network security and intrusion management.

### The AADL in a Nutshell

The SAE AADL provides an opportunity for the embedded real-time systems research community to have a direct impact on the practitioner community. As the AADL becomes the accepted means for modeling, analyzing, and integrating systems based on architectural models, it can become a vehicle for accelerated transition of research results in new analysis techniques by demonstrating the use of research theories in the context of the AADL/UML.

#### References

1. Pam Binns, Matt Englehart, Mike Jackson and Steve Vestal, "Domain Specific Software Architectures for Guidance, Navigation and Control," Honeywell Technology Center, Minneapolis, MN, International Journal of Software Engineering and Knowledge Engineering, Vol6, No. 2, 1996, pages 201-227.

- Peter H. Feiler, Bruce Lewis, Steve Vestal, "Improving Predictability in Embedded Real-time Systems," Carnegie Mellon Software Engineering Institute, CMU/SEI-2000-SR-011, October 2000.

- David J. McConnell, Bruce Lewis and Lisa Gray, "Reengineering a Single Threaded Embedded Missile application onto a Parallel Processing Platform using MetaH," 5<sup>th</sup> Workshop on Parallel and Distributed Real Time Systems, 1996.

- 4. Patrick Farail, Pierre Dissaux, "COTRE a Software Design Workshop", DASIA 2002, May 2002.

- Bran Selic, "Performance Oriented UML", Tutorial, 3<sup>rd</sup> International Workshop On Software and Performance, July 2002.

- 6. Barry Boehm, Overview, Mini Tutorial, http://sunset.usc.edu/research/MBASE/

- 7. Paul Clements, et.al., "Documenting Software Architectures: Views and Beyond", Addison-Wesley, SEI Series in Software Engineering, 2002.

## SESSION 1: MODELS AND ANALYSIS

## **DEPLOYING QOS CONTRACTS IN THE ARCHITECTURAL LEVEL**

Sidney Ansaloni<sup>1</sup>, Alexandre Sztajnberg<sup>2</sup>, Romulo C. Cerqueira<sup>1</sup>, Orlando Loques<sup>1</sup>

<sup>1</sup>Instituto de Computação – Universidade Federal Fluminense (UFF), Rua Passo da Pátria – Niterói – RJ – Brasil; <sup>2</sup>Instituto de Matemática e Estatística – Universidade do Estado do Rio de Janeiro, Rua São Francisco Xavier, 524 / 6018-D – Maracanã – RJ - Brasil

Abstract: This paper presents an approach to describe, deploy and manage software architectures having dynamic functional and non-functional requirements. The approach is centered on an ADL extended with high-level contracts, which are used to specify the non-functional requirements associated to the architecture of a given application. These contracts are also used to configure the infrastructure required to enforce the non-functional requirements and, during the running time, can be used to guide architecture adaptations, in order to keep them valid in face of changes in the supporting environment. The infrastructure required to manage the contracts follows an architectural pattern, which can be directly mapped to specific components included in a supporting reflective middleware. This allows designers to write a contract and to follow standard recipes to insert the extra code required to its enforcement in the supporting middleware.

Key words: QoS contracts ADL, architectural pattern, dynamic configuration

#### 1. INTRODUCTION

The specification of QoS requirements and the implementation of the corresponding management strategies for the resource providers associated to the requirements are, generally, embedded in the application programming in an ad-hoc manner, mixed with the application's specific code. This lack of modularity makes evolution and code reuse difficult, also making difficult its

verification and debugging. In this context, there is a growing interest for handling quality of services (QoS) aspects in a specific abstraction level<sup>1, 2, 3</sup>. This approach would allow to single out the resources to be used and the specific mechanisms of the native system that will be required by the application, and, if possible, turn automatic the configuration and management of those resources.

The traditional notion of QoS is bound to communication level performance. However, a more recent view of OoS includes characteristics associated to application's non-functional aspects, such as availability, reliability, security, real-time, persistency, coordination and debugging support. Such kind of aspect can be handled by reusable services provided by middleware infrastructures or native systems support. This makes feasible to design a software system based on its architectural description, which includes the functional components, the interactions among those components, and requirements regarding the behavior of system QoS resources. To this end, it has to be provided a means to specify those requirements in the context of the application's architecture description and, also, there has to be available an environment that allows to deploy those requirements over the system resources. In some applications, such environment has to include mechanisms to monitor the resources and to manage adaptations, according to the availability of those resources, in order to guaranty that the QoS requirements are met during run-time.

Among the available techniques to specify QoS constraints, we highlight the concept of contracts <sup>4</sup>. A QoS contract establishes a formal relationship between two parts that use or provide resources, where rights, obligations and negotiation rules over the used resources are expressed. For instance, a parallel computing application can have a QoS contract defining rules to replicate processing resources, in order to guaranty a maximum execution time constraint. According to the specified contract, the application can have its components parallelization degree automatically controlled by the supporting environment. Thus, when the time constraint is not being met by the present configuration, the number of replicas can be raised, if there are available processors <sup>5</sup>.

In the previous context, this work presents the CR-RIO framework (*Contractual Reflective - Reconfigurable Interconnectable Objects*)<sup>2,5</sup> conceived to specify and support QoS contracts, associated to the architectural components of an application. The approach helps to achieve separation of concerns<sup>6</sup> facilitating the reuse of modules that implement the computation in other application systems, and allows the non-functional requirements to be handled separately during the system design process. The framework includes a contract description language, which allows the definition of a specialized view of a given software architecture. The

supporting infrastructure required to impose the contracts during run-time follows an architectural pattern that can be implemented by a standard set of components included in a middleware. The results of our investigation point out that the code generation of these components can be automated, except some explicit parts of code related to specific contract and resources classes. In this way, contracts and their respective supporting infrastructures can be reused in different applications.

In the rest of this paper, we initially describe the key elements of the framework including the architecture description language with support to QoS contracts. Next, we present the supporting infrastructure and, based on an example we demonstrate the validity of the framework. Complementing the article we present some related proposals and provide some conclusions.

#### 2. BASIC FRAMEWORK

The CR-RIO framework integrates the software architecture paradigm, which is centered in an architecture description language (ADL), with concepts such as reflection and dynamic adaptation capability<sup>6</sup>, which are generally provided in an isolated fashion in middleware proposals described in the literature. This integration facilitates the achievement of separation of concerns, software component reuse and dynamic adaptation capability of applications. CR-RIO includes the following elements:

CBabel, an ADL used to describe the functional components of the application and the interconnection topology of those components, which follow the CR-RIO model. CBabel also caters for the description of noncoordination, distribution, functional aspects, such as planned reconfigurations and QoS. This set of features turns possible submitting CBabel descriptions to formal verification procedures<sup>7</sup>. A CBabel specification corresponds to a meta-description of an application that is available in a repository and is used to deploy the architecture in a given operating environment. In running time this meta-description provides the information required to manage architectural adaptations.

An architecture-oriented component model, that allows programming the software configuration of the application; (i) Modules, which encapsulate the application's functional aspects; (ii) Connectors, used in the architecture level to define relationships between modules; in the operation level connectors mediate the interaction between modules; and (iii) Ports, which identify access points through which modules and connectors provide or require services; ports are fundamental to allow component linking with low coupling. A simple **software design methodology** that encourages the designer to follow a simple meta-level programming discipline, where functional aspects are concentrated in modules (base level) and non-functional aspects are encapsulated in connectors (meta-level). It is worth to point out that some QoS requirements can be directly mapped into connectors, which are equivalent to meta-level components, and can be configured in an application's architecture. For example, the access to real-time communication mechanisms, such as a real-time RMI<sup>8</sup>, could be encapsulated into a connector and configured in different architectures.

The **Configurator**, a reflective element that provides services to instantiate, execute and manage applications with distributed configurations. The Configurator provides two APIs: configuration and architectural reflection, through which these services are used, and a persistency mechanism for the architecture meta-level description repository, where the two APIs reflect their operations. The configuration API allows to *instantiate*, *link*, *stop* and *replace* components of a running application. The architectural reflection API allows querying the repository. A specialized module of the application can consult the architecture's configuration and decide to make changes under certain conditions, say, in face of resource changes.

To specify non-functional aspects or quality of service (QoS) aspects related to operational requirements such as processing capacity, fault tolerance, real-time, information persistency, security or communication CBabel employs the concept of architectural contract. In our approach, an architectural contract is a description where two parts express their nonfunctional requirements, through services and parameters, negotiation rules and adaptation policies for different contexts. The CR-RIO framework provides the required infrastructure to impose and manage the contracts during run-time. Regarding QoS aspects we propose an architectural pattern that simplifies the design and coding of specific components of the infrastructure, consistently establishing the relationship between the Configurator and the QoS contract supporting entities.

#### 3. THE QOS ARCHITECTURAL PATTERN

In our proposal a functional service of an application is considered a specialized activity, defined by a set of architectural components and theirs interconnection topologies; with requirements that generally do not admit negotiation<sup>1</sup>. Non-functional services are defined by restrictions to specific non-functional activities of an application, and can admit some negotiation including the used resources. A contract regulating non-function aspects can

describe, at design time, the use of shared resources the application will make and acceptable variations regarding the availability of these resources. The contract will be imposed at run-time by an infrastructure composed by a set of components that implement the semantics of the contract.

#### 3.1 The QoS Contract Language

Our proposal incorporates concepts from the QML (QoS Markup Language)<sup>4</sup>, which were reformulated for the context of software architecture descriptions<sup>2</sup>. A QoS contract includes the following elements:

**QoS Categories** are related to specific non-functional aspects and described separately from the components. For example, if processing and communication performance characteristics are critical to an application, associated categories, *Processing* and *Transport*, could be described as in Figure 1.

| 01 | <b>QoScategory</b> Processing {                  |

|----|--------------------------------------------------|

| 02 | utilization: decreasing numeric %;               |

| 03 | clockFrequency: increasing numeric MHz;          |

| 04 | <pre>priority: increasing numeric; }</pre>       |

| 05 | <b>QoScategory</b> Transport {                   |

| 06 | delay: decreasing numeric ms;                    |

| 07 | <pre>bandwidth: increasing numeric Mbps; }</pre> |

|    |                                                  |

Figure 1. Processing and Transport QoS Categories

The Processing category (lines 1-5) represent a processing resource where the utilization property is the used percentage of the total CPU time (low values are preferred – decreasing), the *clockFrequency* property represents the processor's operating frequency (high values are preferred – increasing) and priority represents a priority for its utilization. The Transport category (lines 5-7) represents the information associated to transport resources used by clients and servers. The *bandwidth* property represents the available bandwidth for the client-server connection and the *delay* property represents the transmission delay of one bit between a client and the server. The use of those categories, and of the other elements of the language described next, is presented in Section 4.

A **QoS profile** quantifies the properties of a QoS Category. This quantification restricts each property according to its description, working as an instance of acceptable values for a given QoS Category. A component, or a part of an architecture, can define QoS profiles in order to constrain its operational context.

A set of services can be defined in a contract. In a service, QoS constraints that have to be applied in the architectural level are described,

and can be associated to either (i) the application's components or (ii) the interaction mechanism used by these components. In that way, a service is differentiated from others by the desired/tolerated QoS levels required by the application, in a given operational context. A QoS constraint can be defined by associating a specific value of a property to an architecture declaration or associating a QoS profile to that declaration.

A **negotiation clause** describes a negotiation policy and acceptable operational contexts for the services described in a contract. As a default policy the clause establishes a preferred order for the utilization of the services. Initially the preferable service is used. According to the described in the clause, when a preferable service cannot be maintained anymore, the QoS supporting infrastructure tries to deploy a service less preferable, following the described order. The supporting infrastructure can deploy a more preferable service again if the necessary resources are again available.

#### 3.2 Support Architecture

CBabel described architectures and QoS contracts are stored as metalevel information. Based on this information a set of middleware components (see Figure 4) composing a well-defined architectural pattern<sup>2</sup> is used to instantiate the application and to manage the contracts.

The Global Contract Manager (GCM) interprets a contract description and extracts its service negotiation state machine. When a negotiation is initiated the GCM identifies which service will be negotiated first and sends the configuration descriptions, related to each participating node, and the associated QoS profiles to the Local Contract Managers (LCM). Each LCM is responsible for interpreting the local configuration and activating a *Contractor* to perform actions such as resources reservation and monitoring requests. If the GCM receives a positive confirmation from all LCM involved, the service can be attended and the application can be instantiate with the required quality. If not, a new negotiation is attempted in order to deploy the next possible service. If all services in the negotiation clause are tried with no success, an *out-of-service* state is reached and a contract violation message is issued to the application level. The GCM can also initiate a new negotiation when it receives a notification informing that a preferred service became available again.

The **Contractor** has several responsibilities: (a) to translate the properties defined by the QoS profiles into services of the support system and convey the request of those services (with adequate parameters) to the QoS Agents; (b) when required, to map each defined interaction scheme (*link*) into a connector able to match the required QoS for the actual interaction, and (c) to receive *out-of-spec notifications* from the QoS Agents.

The information contained in a notification is compared against the profile and, depending on its internal programming the Contractor can try to make (local) adjustments to the resource that provides the service. For instance, the priority of a streamer could be raised in order to maintain a given frame generation rate. In a case where this is not possible an *out-of-profile* notification is sent to the LCM.

A **QoS Agent** wraps the access to system level mechanisms, providing adequate interfaces to perform resource requests, initializes local system services and monitors the actual values of the required properties. According to the thresholds to be monitored, registered by the Contractor, a QoS Agent can issue an *out-of-spec* notification indicating that a resource is not available or does not meet the specification defined in the profile.

#### 4. EXAMPLE

During our research we developed some prototype examples to evaluate and refine the framework. A virtual terminal in a mobile machine was used to evaluate security and communication aspects in the context of a mobile network<sup>9</sup>. Specifically, a static contract was used to specify security protocol options (*telnet* or *ssh*, and cipher types) and a dynamic contract was used to specify communication channels that can be dynamically reconfigured (reconfiguration can be triggered by changes in available set of channels); in this example it was also demonstrated the composition of both contracts, which was immediately achieved joining theirs negotiation clauses. We developed in <sup>5</sup> the application with real-time requirements, mentioned in the introduction, an application with fault tolerance requirements, and the video on demand application to be presented in the next subsections.

#### 4.1 Video on Demand (VoD)

The scenario of the application is comprised by a server, which stores a collection of video files in the MPEG-2 format, and by clients that connect themselves to the server and initialize a flow to receive and display a selected video. Each client can freeze or resume the video exhibition, in the same way it would be done if the video were locally stored. It is assumed that the clients can run on different platforms, from portable devices to workstations, in which the availability of resources such as CPU capacity and bandwidth can vary. In this context it is necessary to adapt the resources or the application's architecture configuration, depending on the specific operational environment, in order to have the video being exhibited with the expected quality.

The basic architecture of the example should fit two types of client: (i) high processing availability, with high-speed access to the server and (ii) medium processing availability, with dial-up modem access to the server. In principle, clients of type (i) have enough processing and communication resources to exhibit the video in the original MPEG-2 format. Clients of type (ii), with limited resources, can only exhibit the video in and alternative format, say H.261.

```

module Client Server {

01

02

port provide, request;

module Client { out port request; } player;

03

04

module Server { in port provide; } server;

instantiate server at serverHost;

05

06

instantiate player;

07

link player.request to server.provide;

80

} vod;

09

start vod;

```

Figure 2. VoD application Architecture Description

Figure 2 presents the CBabel description of the application's architecture, composed by a client (*player* - line 3) and a server (*server* - line 4), and their connection topology; communication is made effective through the player's *request* port and the server's *provide* port (lines 5-7). Note that this interconnection could be detailed, by defining a specific connector to mediate the client-server interaction, encapsulating the necessary communication mechanisms. However, as the non-functional restrictions include interaction aspects, the use of connectors in this architecture will be defined explicitly in a contract.

#### 4.2 **QoS Contract**

The QoS contract of this example considers that two services can be used: (i) the exhibition of the video in the MPEG-2 format or (ii) in the H.261 format, according to the availability of resources at the specific client platform. To deploy any of these services in the client's node, the resources to be handled are those related to the host's processing characteristics and to the client-server communication channel properties.

The QoS categories for processing and transport, and their properties to specify the VoD application contract, are those presented previously in Figure 1. In the example it is considered that the client has to have a CPU with a minimum operating frequency of 700 MHz and a maximum of 50% of used CPU time to exhibit video in the MPEG-2 format. The exhibition of video with the H.261 format will demand from the CPU, by its turn, only a

minimum frequency of 266 MHz and a maximum CPU time usage of 70%. In the example we are not considering static reservation of CPU time, in order to illustrate a contract renegotiation activity. Please note that in a dynamic context, even with CPU reservation, a contract could be invalidated by another contract with higher priority.

In the example, the MPEG-2 requires a bandwidth greater than 1.5 Mbps and a transport delay lower than 50 ms to sustain an acceptable video stream, while videos in H.261 format require a minimum bandwidth of 56 Kbps and can tolerate delays up to 200 ms. Other transport properties could be taken into account in this case, such as the *jitter* or data loss rate; for the sake of simplicity they were not included in the *Transport* QoS Category.

```

01

contract {

02

service {

03

instantiate player at clientHost with cpu 01;

link player to server by comTransport with network 01;

04

05

} MPEG video;

06

service {

instantiate player at clientHost with cpu_02;

07

80

link player to server by H-261.comTransport

with network 02;

09

10

} H-261 video;

negotiation {

11

12

MPEG_video -> H-261_video;

H-261 video -> out of service;

13

14

}

15

} vod;

16

profile {

Processing.clockFrequency >= 700;

17

Processing.utilization <= 50;</pre>

18

19

} cpu 01;

20

profile {

21

Processing.clockFrequency >= 266;

22

Processing.utilization <= 70;

23

} cpu 02;

24 profile {

25

Transport.delay <= 50;</pre>

26

Transport.bandwidth >= 1.5;

27

} network 01;

28

profile {

29

Transport.delay <= 200;</pre>

Transport.bandwidth >= 0.056;

30

// 56 kbps

31

} network 02;

```

Figure 3. VoD application QoS Contract

Based on the previous requirements the application's contract can be described as in Figure 3. The *MPEG\_video* service (lines 2-5) defines the QoS constraints for the architecture parts that participate in the MPEG video

exhibition. The creation of a player component instance (line 3) in a client machine is associated to the cpu 01 processing QoS profile. The interconnection of the player and server ports are bound to the network\_01 QoS profile (lines 25-27), being the communication provided by a connector that encapsulates the communication transport mechanism (line 4). The mentioned profiles specify, respectively, the constraints to the Processing and Transport QoS Categories properties, relevant to this contract. Thus, to create the player instance, the *clockFrequency* of the node has to be at least 266 MHz and then the CPU utilization has to be less than 70%. The H-261 video service description follows a similar procedure. The cpu 02 (lines 20-23) and network 02 (lines 28-31) profiles represent the requirements for the H.261 video exhibition. Note that, for this service, the interaction of the components is mediated by a connector that encapsulates the MPEG-2 to H-261 conversion mechanism. Additionally to the MPEG-2 and H.261, other formats could be supported by using specific decoders, encapsulated in connectors; e.g., the bitmap format that can be exhibited on PDAs and cellphone video matrixes.

The negotiation clause of this contract (lines 11-14) defines the priority order between the services. The  $MPEG\_video$  service has to be preferably provided in relation to the  $H-261\_video$  service. If there are no resources available to attend any of these services, an *out-of-service* state is reached and the application cannot run.

#### 4.3 Mapping the contract into the architectural pattern

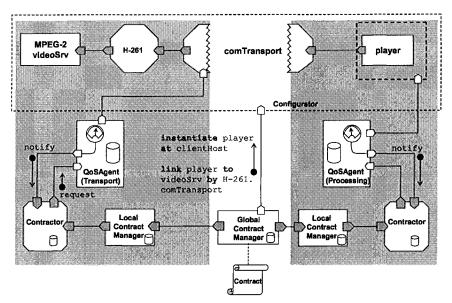

The implementation of the QoS contract of the example-application using the proposed architectural pattern is depicted in Figure 4. Each participant node has a running instance of the *Local Contract Manager*, the specific *Contractor* for the VOD application and *QoS Agents* associated to the resources to be controlled in each specific platform. The *Configurator* (Section 2) and the *Global Contract Manager* can be instantiated in a node dedicated to manage applications or in the same node were the application's server is running. The *H-261* connector only takes part of the configuration when the *H-261\_video* service is deployed. It can also be observed that the *comTransport* connector has a distributed implementation.

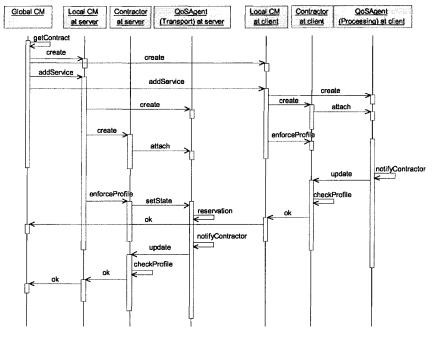

The sequence diagram presented in Figure 5 depicts the interactions between the CR-RIO components to establish the MPEG\_video service to a player running in a node, which is connected to the server through an Ethernet network. When starting the procedure to load the application the Configurator and the GCM are already running. As the first step, the GCM retrieves the associated QoS contract; all further actions are guided by this contract. Initially the GCM creates instances (create()) of the LCM in the nodes where the application components are to be instantiated. Next, it selects a service to be used (in this case, the MPEG\_video) and initializes a negotiation activity, sending to the LCMs the information related to this service, including the associated QoS profiles (cpu\_01 and network\_01). Each LCM extracts from the received information the QoS characteristics that have to be considered and instantiates (*create()*) (a) the QoS Agents that provide the interfaces (management and event generation) to the resources used by the service, and (b) the application specific Contractor, that will interpret the service information and will interact with the QoS Agents to impose the desired properties.

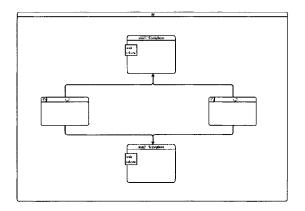

Figure 4. Mapping the VoD application contract in the architectural pattern

In the client node, the LCM identifies the processing resources that have to be managed (based on the *instantiate* ADL's primitive that creates an instance of the *player* module – QoS contract, line 3). In the server node, the local LCM identifies (based on the *link* ADL's primitive that interconnects the *player* module to the *server* module – QoS contract, line 4) that it will be responsible for the management of the transport resources (the adopted semantics is to assign to the server side the responsibility for managing QoS requirements that involves two peers). When the LCM instantiates a Contractor it also sends to it the profiles that have to be attended. In the sequence, the Contractor interacts with the QoS Agents to request resources and to receive relevant events regarding the status of the resources. In this example, the *Processing* QoS Agent verifies the operating frequency of the CPU and is responsible for monitoring the CPU load (*utilization*). Also, observe that the client-server communication channel uses some kind of resource reservation put in effect through the *Transport* QoS Agent.

Figure 5. Establishing the MPEG\_video service

After the initial phase, if the required QoS profiles were imposed, a Contractor notifies the success to its associated LCM that, by its turn, forwards a corresponding notification to the GCM. In the example, if all involved LCMs did return a positive confirmation, the GCM concludes that the negotiation was successful and that the *MPEG\_video* service can be established. The next step is to instantiate the application's functional components in the context of the reserved resources and, then, to initialize its execution. This step is performed by the *Configurator* (Section 2) based on the *Architecture Configurator* design pattern<sup>10</sup>; see details in<sup>5</sup>. If during the negotiation any Contractor has a resource demand denied, or if it verifies that a QoS Agent notified an out of range value, an *out-of-profile* notification is sent to the LCM that, by its turn, sends an *out-of-service* notification to the GCM. In consequence the GCM selects the next service to be attempted, in this case the *H-261 video*, and a new negotiation cycle begins.

In steady state, if a significant change in the monitored values is detected, the QoS Agent notifies the registered Contractors invoking the *update()* method. If the reported values do not violate the active QoS profiles, nothing

has to be done. If there is a violation, the Contractor can try to locally readapt the resource in order to keep the service; for instance, passing new parameters to the QoS Agent. If it is not possible to readapt, the Contractor sends an *out-of-profile* notification to the LCM and, in the sequence, another service can be negotiated. To exemplify the situation let's suppose that while the *MPEG\_video* is operational, new processes are admitted to the client's node, diminishing the available processing power to the player. This would be captured by the *Processing* QoS Agent observing the increase of the value of the *utilization* property. Let's consider that the measured value overcomes the limit of 50% defined by the *cpu\_01* profile, but is still lower than the 70% limit defined by the *cpu\_02* profile.

The Processing QoS Agent notifies the Contractor triggering a new negotiation. The client's Contractor verifies that the property is out of the cpu 01 profile specification and sends the respective LCM an out-of-profile notification. This information is then propagated to the GCM through an outof-service notification. Then the GCM selects the H-261 video to be negotiated and sends the respective information as parameters invoking to the involved LCMs. Each LCM discontinues the current service and the procedures to impose the new service, bound by the cpu 02 and network 02 QoS profiles are performed (similarly as in the case to deploy the initial service). Several optimizations are feasible. For instance, when a Contractor sends an out-of-profile notification this could be followed by the set of QoS profiles that could be attended at that moment. Receiving this composed information the GCM could select the next service to be negotiated, immediately discarding the services with associated profiles out of the set. We are investigating the use of an event support service, with composition capability, to implement this optimization. A second optimization could be applied when a set of services is restricted to a given node. In this case the LCM of the given node could receive the information of all services and profiles related to the set and manage them locally.

A prototype of the VoD application is presented in<sup>5</sup>. The Java *Media Framework* was used to implement the functional modules. Some classes related to the video flow were encapsulated in connectors, e.g., those implementing RTP and the H.261 codec. The QoS architectural pattern was implemented as a set of classes integrated to the CR-RIO framework.

It was possible to identify that the implementations of the GCM and the LCM, directly related the application contract are reusable. The behavior of these elements is parameterized by the QoS contract of the specific application; in this level the manipulated information are symbolic. Each QoS Agent has dependencies related to the resource being managed. However, once implemented, an Agent can be reused in other applications that have operational requirements dependent on the same kind of resource.

The Contractor, by its turn, represents the *hot spot* of the pattern. Its implementation is dependent on the services and profiles to be imposed, and also dependent on the own resources to be managed via QoS Agents. The Contractor can also contain the code implementing specific policies to perform local adaptations, as discussed in the end of the last section.

# 5. RELATED WORKS

The reflective middleware approach<sup>11</sup> allows for the provided services to be configured to comply with the non-functional properties of the applications. However, the approach does not provide clear abstractions and mechanisms to help the use of such features in the design of the architectural level of an application. This leads to the middleware services being used in an ad hoc fashion, usually through pieces of code intertwined to the application's program. The Quality Connector pattern provides a methodology for the re-allocation of resources in response to context changes in the execution environment<sup>12</sup>. However, it requires access to the source code of every application and/or to the infrastructure's components in order to instrument them. Our approach, that includes configurationprogramming mechanisms, is more transparent regarding the access to the source code of the application. The Quality Objects (QuO)<sup>3</sup> provides a framework for the development of distributed applications with QoS requirements, based on CORBA. In QuO, the specification of such requirements is associated to method invocations, through a contract description language, allowing only adaptations at this level. Our proposal considers services with differentiated quality in diverse levels, from the interface (or connection) level, in which services are encapsulated into connectors (similar to the QuO approach), to the architectural level, in which the service provision can involve the reconfiguration of the application's topology. The proposal described in<sup>13</sup> includes basic mechanisms to collect status information associated to non-functional services. It also suggests an approach to manage non-functional requirements in the architectural level, in a way quite similar to ours. CR-RIO complements this proposal providing an explicit methodology based on contracts and proposing extra mechanisms to deploy and manage these contracts. More details are available in<sup>5</sup>.

# 6. CONCLUSION

We presented a unified approach to specify, deploy and manage applications having non-functional requirements. The approach helps to achieve separation of concerns and software reuse by allowing nonfunctional aspects of an application, such as OoS requirements, to be specified separately using high-level contracts expressed in an extended ADL. Being centered on an ADL-based configuration middleware the framework inherits all its well-known benefits, among them the capability of reconfiguration, which facilitates to execute dynamic architectural adaptations on behalf of a contract. Part of the coding, related to a nonfunctional requirement, can be encapsulated in connectors, which can be (re)configured during running time in order to cater for the impositions defined by the associated contract. The infrastructure required to enforce the contracts follows an architectural pattern that is implemented by a standard set of components of the middleware. In this pattern, each component performs a well-defined role in the support of the contract. We think that making these structures explicit and available to designers, the task of mapping architecture-level defined contracts to implementations can be simplified. The approach has been evaluated through several case studies that showed that the code of these supporting components can be automatically generated, excepting some localized pieces related to specificities of the particular QoS requirement under consideration. However, we should notice that the treatment of low-level details always has to be considered in any QoS aware application. Our approach can help to identify the intervening hot spots and to make adaptations more rapidly.

In our proposal, the composition of contracts can be specified combining in a unique clause the negotiation clauses of the involved contracts<sup>9</sup>. Contracts regarding different non-functional aspects (in the same or in different applications) can be orthogonal and cause no interference with each other; in this case, composing those contracts is immediate. In the general case, the composition process can lead to conflicts on the use of shared scarce resources. Conflicts can be handled applying a suitable decision policy to the set of involved contracts; already assigned resources could then be retaken in order to satisfy the preferred contracts.

Currently, we are investigating the specification of individual contracts for clients and servers<sup>14</sup>. This intends to allow each client to specify what it requires and each server to specify what it is committed to provide. This capability would permit to make decisions regarded to a component instantiation taking into account the availability of resources at its instantiation time. Besides providing the flexibility required to the support of dynamic architectures, this would allow managing conflicts through lower granularity interventions. We are also working towards giving a formal semantics to the QoS contracts, using Rewriting Logic, in the same line as presented in<sup>7</sup> for the CBabel ADL. With the results of that experience we plan to produce a set of guide-lines to allow the formal verification of the QoS contracts in the architectural level.

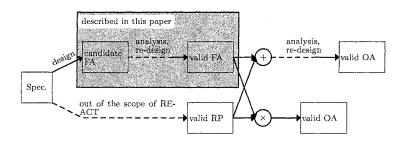

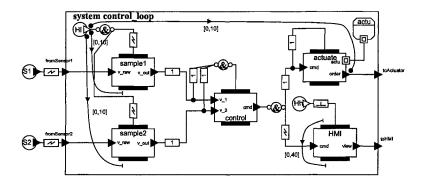

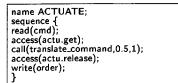

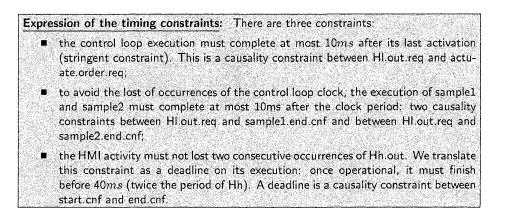

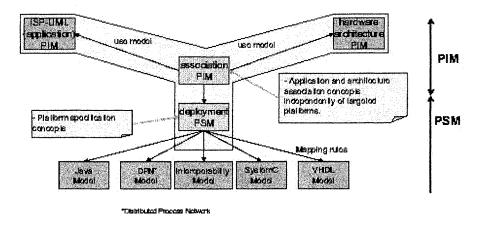

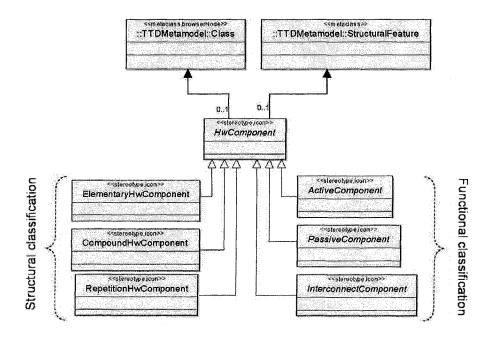

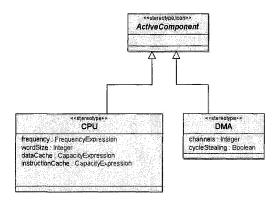

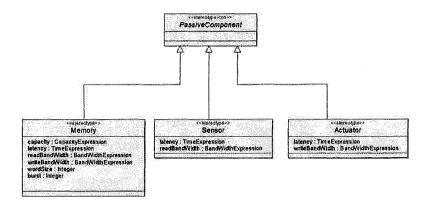

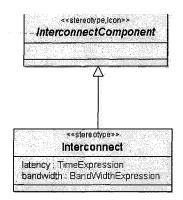

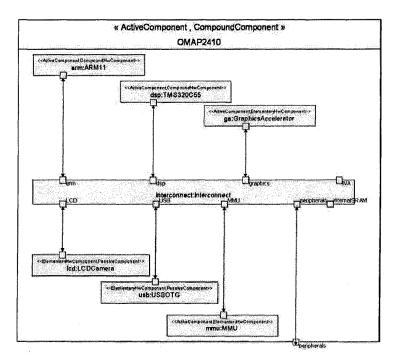

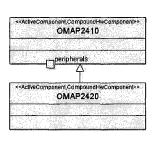

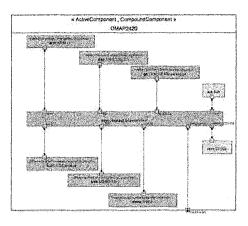

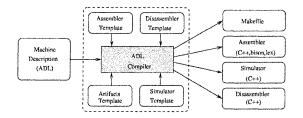

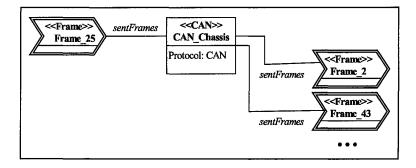

### ACKNOWLEDGMENTS